## Computer Science 146 Computer Architecture

Fall 2019 Harvard University

Instructor: Prof. David Brooks dbrooks@eecs.harvard.edu

#### Prerequisites

- CS141 (Computing Hardware) or similar

- Logic Design (computer arithmetic)

- Basic ISA (what is a RISC instruction)

- Pipelining (control/data hazards, forwarding)

- Will review the above during the first couple of weeks

- C Programming, UNIX

- Compilers, OS, Circuits/VLSI background is a plus, not needed

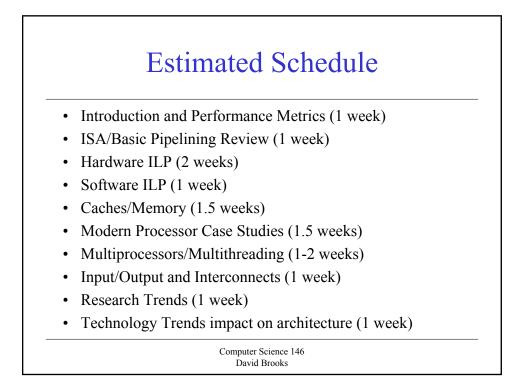

# Topics of Study

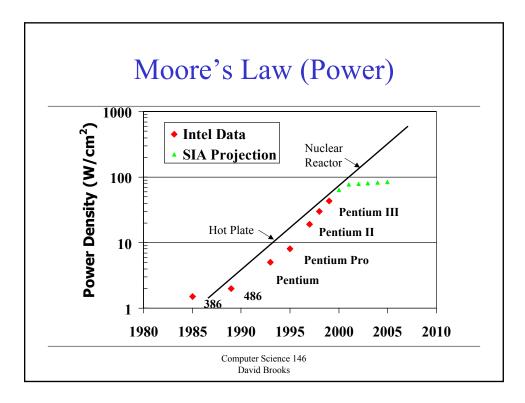

- Focus on what modern computer architects worry about (both academia and industry)

- Get through the basics of modern processor design

- Understand the interfaces between architecture and system software (compilers, OS)

- System architecture and I/O (disks, memory, multiprocessors)

- Look at technology trends, recent research ideas, and the future of computing hardware

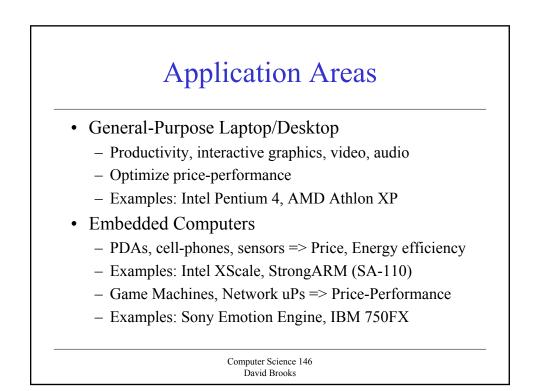

## **Application Areas**

- Commercial Servers

- Database, transaction processing, search engines

- Performance, Availability, Scalability

- Server downtime could cost a brokerage company more than \$6M/hour

- Examples: Sun Fire 15K, IBM p690, Google Cluster

- Scientific Applications

- Protein Folding, Weather Modeling, CompBio, Defense

- Floating-point arithmetic, Huge Memories

- Examples: IBM DeepBlue, BlueGene, Cray T3E, etc.

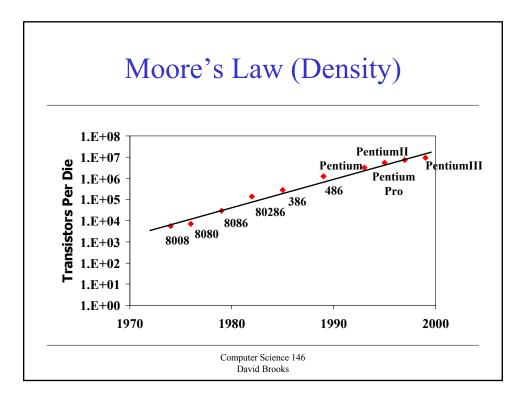

#### How have we used these transistors?

- More functionality on one chip

- Early 1980s 32-bit microprocessors

- Late 1980s On Chip Level 1 Caches

- Early/Mid 1990s 64-bit microprocessors, superscalar (ILP)

- Late 1990s On Chip Level 2 Caches

- Early 2000s Chip Multiprocessors, On Chip Level 3 Caches

- What is next?

- How much more cache can we put on a chip? (IRAM)

- How many more cores can we put on a chip? (Piranha, etc)

- What else can we put on chips?

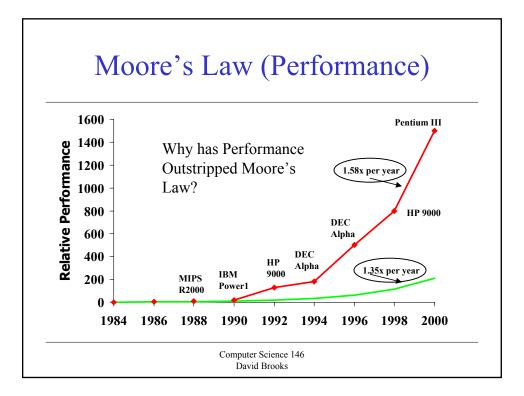

#### Performance vs. Technology Scaling

- Architectural Innovations

- Massive pipelining (good and bad!)

- Huge caches

- Branch Prediction, Register Renaming, OOO-issue/execution, Speculation (hardware/software versions of all of these)

- Circuit Innovations

- New logic circuit families (dynamic logic)

- Better CAD tools

- Advanced computer arithmetic

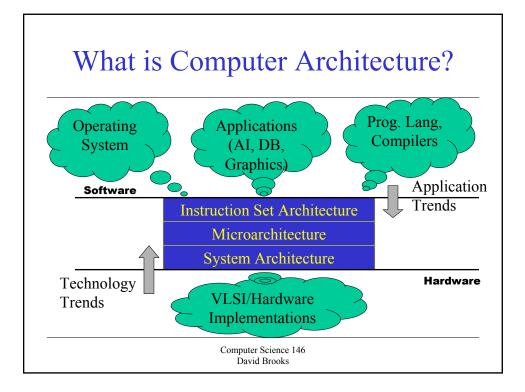

## Dealing with Complexity: Abstractions

- As an architect, our main job is to deal with tradeoffs

- Performance, Power, Die Size, Complexity, Applications Support, Functionality, Compatibility, Reliability, etc.

- Technology trends, applications... How do we deal with all of this to make real tradeoffs?

- Abstractions allow this to happen

- Focus is on metrics of these abstractions

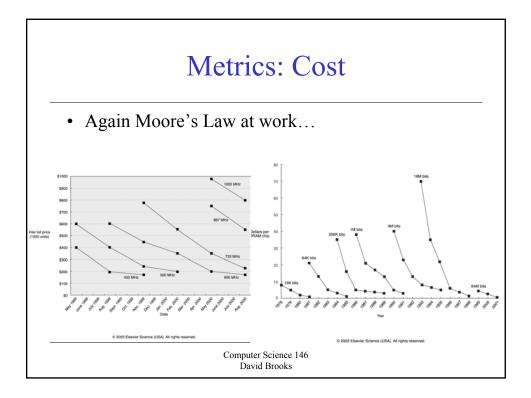

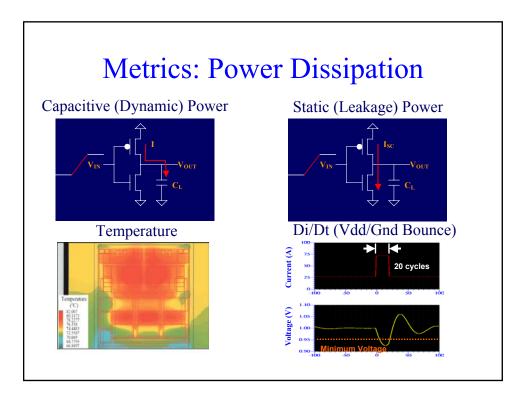

- Performance, Cost, Availability, Power