# Computer Science 146 Computer Architecture

Fall 2019 Harvard University

Instructor: Prof. David Brooks dbrooks@eecs.harvard.edu

Lecture 16: Even more on Caches

David Brooks

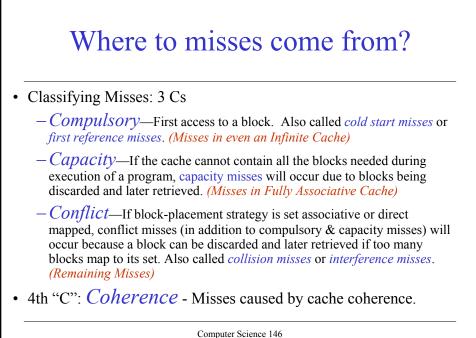

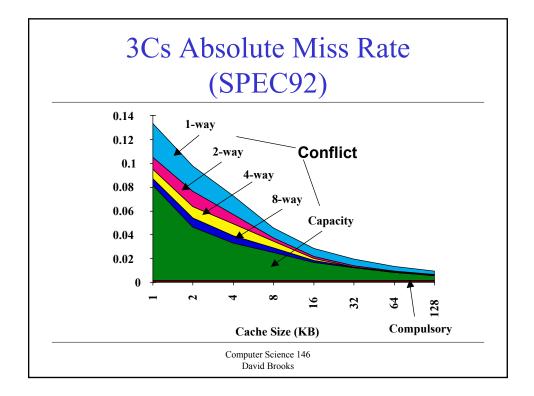

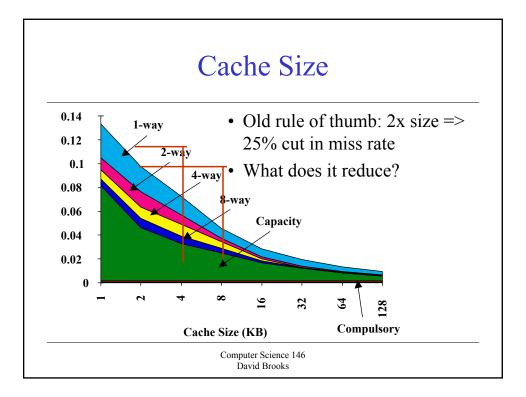

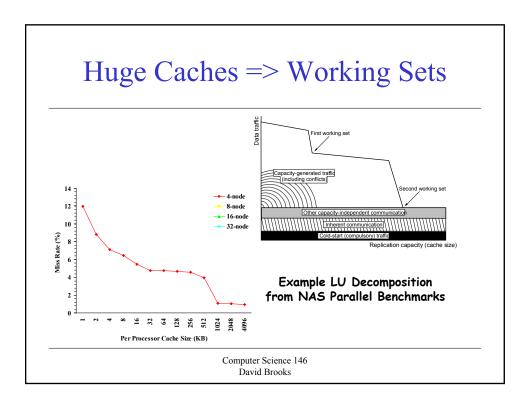

## Cache Organization?

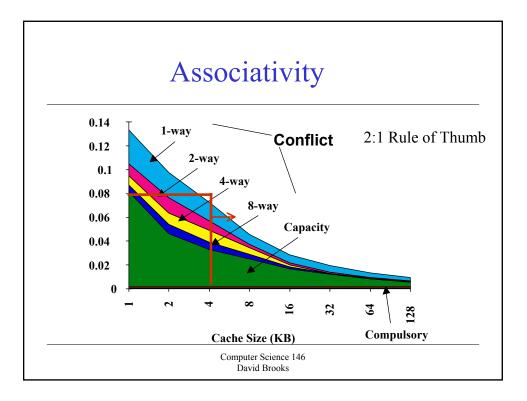

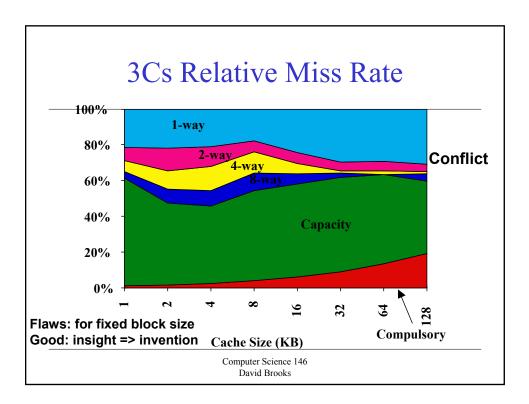

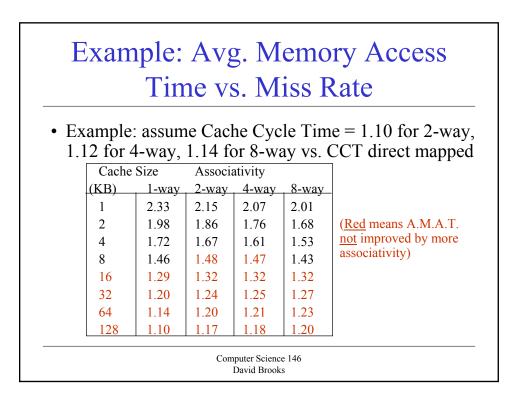

- Assume total cache size not changed:

- What happens if:

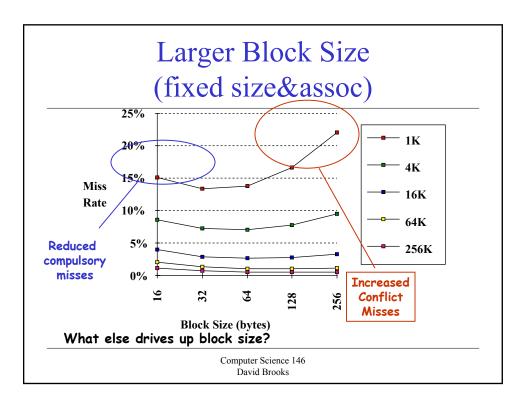

- 1) Change Block Size:

- 2) Change Associativity:

- 3) Change Compiler:

Which of 3Cs is obviously affected?

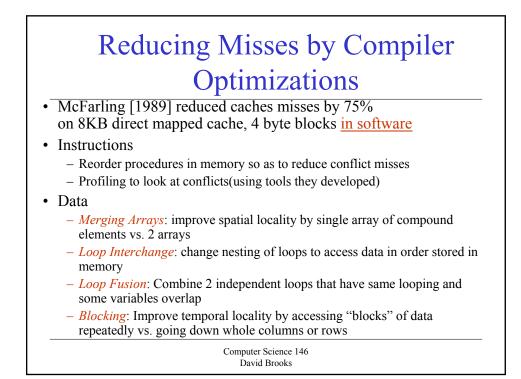

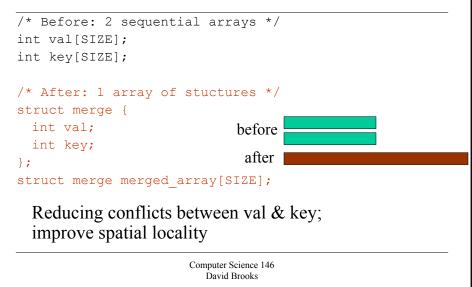

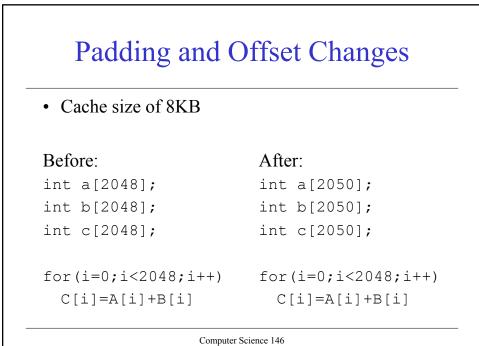

## Merging Arrays Example

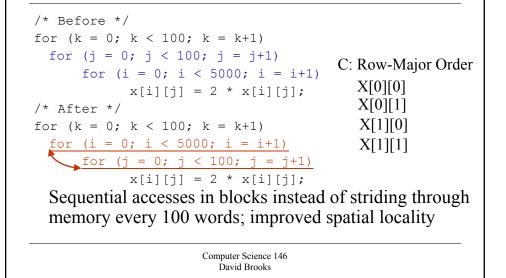

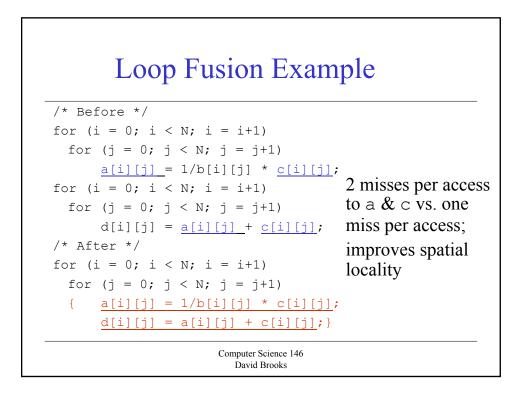

### Loop Interchange Example

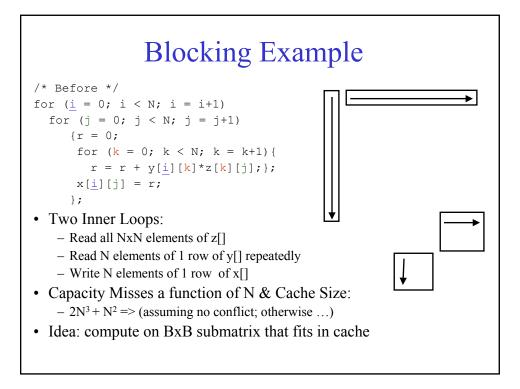

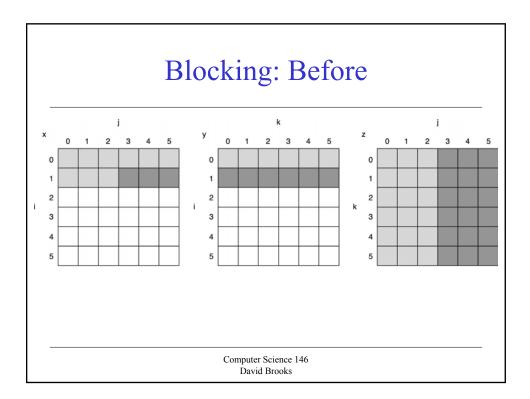

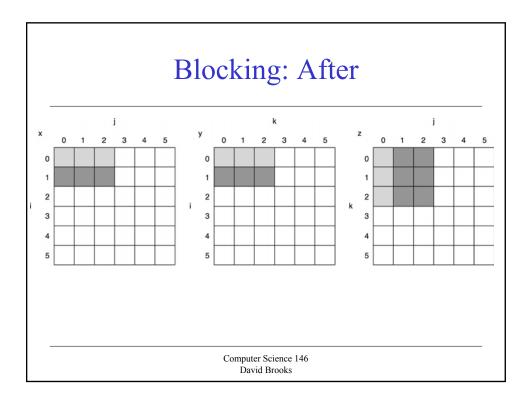

## **Blocking Example**

```

/* After */

for (jj = 0; jj < N; jj = jj+B)

for (kk = 0; kk < N; kk = kk+B)

for (i = 0; i < N; i = i+1)

for (j = jj; j < min(jj+B-1,N); j = j+1)

{r = 0;

for (k = kk; k < min(kk+B-1,N); k = k+1) {

r = r + y[i][k]*z[k][j];};

x[i][j] = x[i][j] + r; };

• B called Blocking Factor</pre>

```

- Capacity Misses from  $2N^3 + N^2$  to  $N^3/B+2N^2$

- Conflict Misses Too?

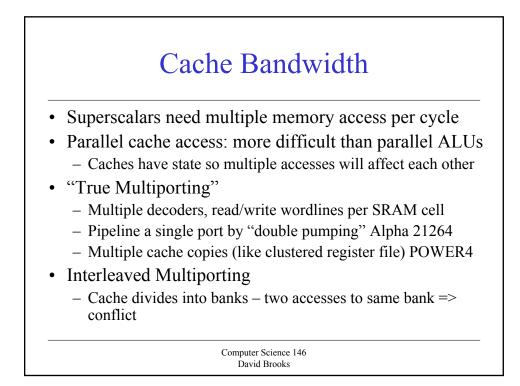

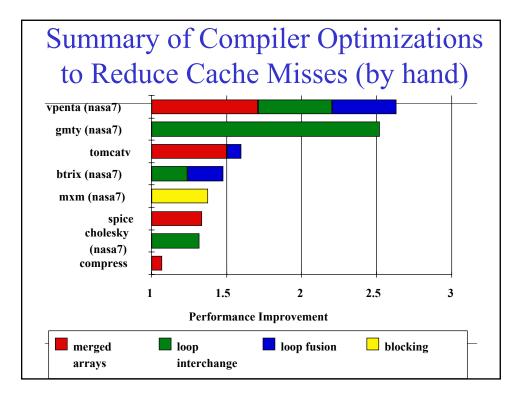

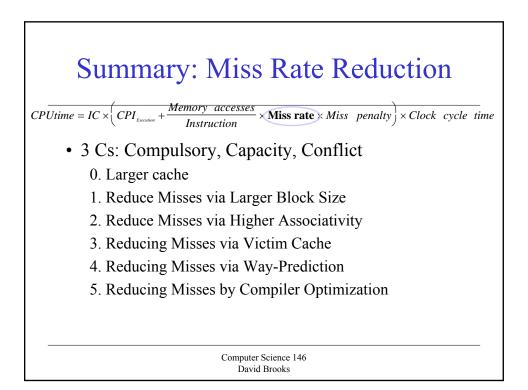

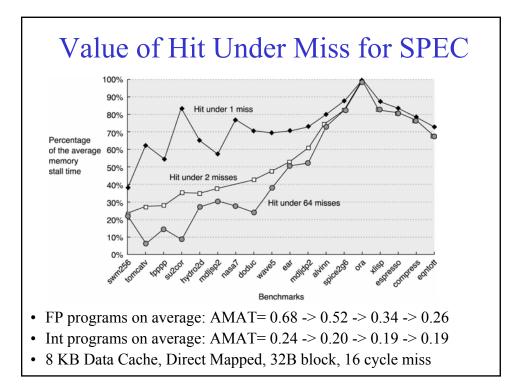

# Performance How to improve cache performance? Reducing Cache Miss Penalty Reducing Miss Rate Reducing Miss Penalty/Rate via parallelism Reducing Hit Time

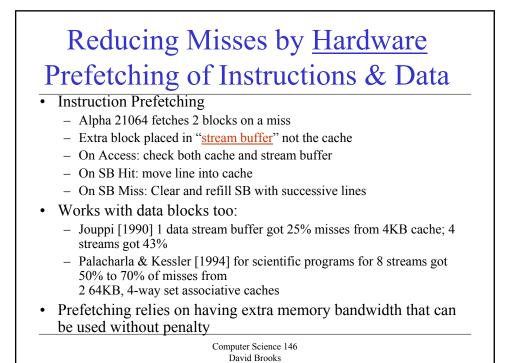

# Hardware Prefetching

- What to prefetch?

- One block ahead (spatially)

- What will this work well for?

- Address prediction for non-sequential data

- Correlated predictors (store miss, next\_miss pairs in table)

- Jump-pointers (augment data structures with prefetch pointers)

- When to prefetch?

- On every reference

- On a miss (basically doubles block size!)

- When resident data becomes "dead" -- how do we know?

- No one will use it anymore, so it can be kicked out

Computer Science 146 David Brooks

# Reducing Misses by Software Prefetching Data

- Data Prefetch

- Load data into register (HP PA-RISC loads)

- Cache Prefetch: load into cache (MIPS IV, PowerPC, SPARC v. 9)

- Special prefetching instructions cannot cause faults; a form of speculative execution

- Prefetching comes in two flavors:

- Binding prefetch: Requests load directly into register.

- Must be correct address and register!

- Non-Binding prefetch: Load into cache.

- Can be incorrect. Faults?

- Issuing Prefetch Instructions takes time

- Is cost of prefetch issues < savings in reduced misses?

- Higher superscalar reduces difficulty of issue bandwidth

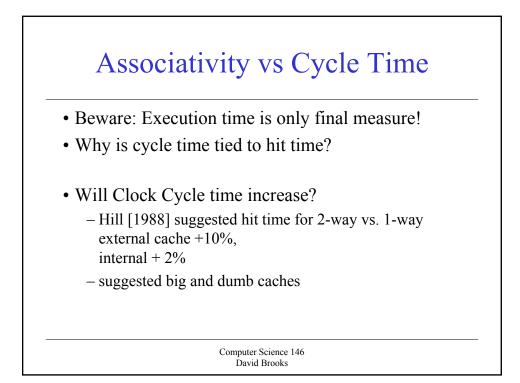

# **Reducing Hit Times**

- Some common techniques/trends

- Small and simple caches

- Pentium III 16KB L1

- Pentium 4 8KB L1

- Pipelined Caches (actually bandwidth increase)

- Pentium 1 clock cycle I-Cache

- Pentium III 2 clock cycle I-Cache

- Pentium 4 4 clock cycle I-Cache

- Trace Caches

- · Beyond spatial locality

- Dynamic sequences of instruction (including taken branches)

# Cache Optimization Summary

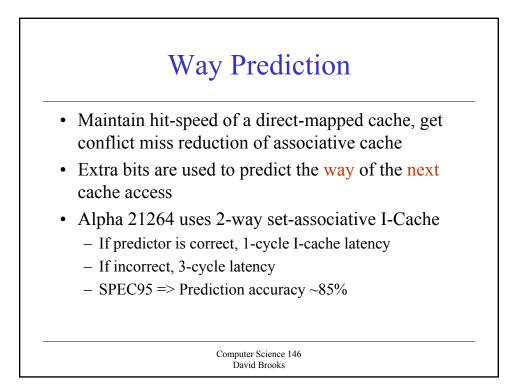

|                 | Technique                         | MR | MP HT | Complexity |

|-----------------|-----------------------------------|----|-------|------------|

| miss rate       | Larger Block Size                 | +  | _     | 0          |

|                 | Higher Associativity/Larger Cache | +  | _     | 1          |

|                 | Victim Caches                     | +  |       | 2          |

|                 | Way-Predicting Caches             | +  |       | 2          |

|                 | HW Prefetching of Instr/Data      | +  | +     | 2          |

|                 | Compiler Controlled Prefetching   | +  | +     | 3          |

|                 | Compiler Reduce Misses            | +  |       | 0          |

| Miss<br>penalty | Priority to Read Misses           |    | +     | 1          |

|                 | Early Restart & Critical Word 1st |    | +     | 2          |

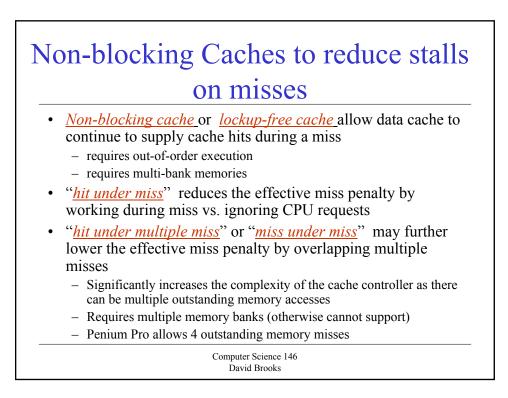

|                 | Non-Blocking Caches               |    | +     | 3          |

|                 | Second Level Caches               |    | +     | 2          |

| Hit<br>time     | Pipelined Cache                   |    | +     | 1          |

|                 | Trace Cache                       |    | +     | 3          |

|                 | Computer Scier<br>David Bro       |    |       |            |